The DPR process requires a certain amount of time to transfer the reconfiguration file, commonly called bitstream (BS), from the external memory to the FPGA reconfiguration area (i.e., FPGA reconfiguration memory).

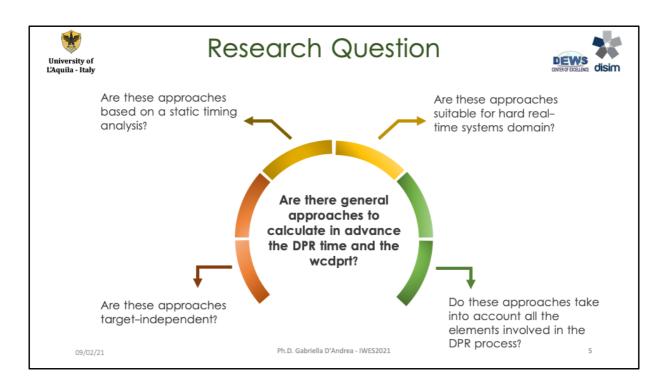

At this time our question is: are there general approaches to calculate the DPR time before the start of the reconfiguration process?

And, if such approaches exist, are they suitable for hard real-time systems? Are these approaches based on a static timing analysis (i.e., an analysis that can be performed at design time)? Are these approaches target-independent, hence potentially applicable to all DPR compliant platforms? And finally, do these approaches take into account all the elements involved in the DPR process?

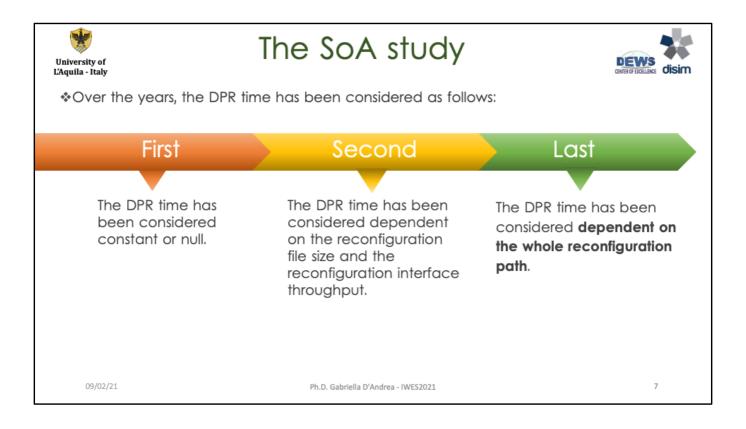

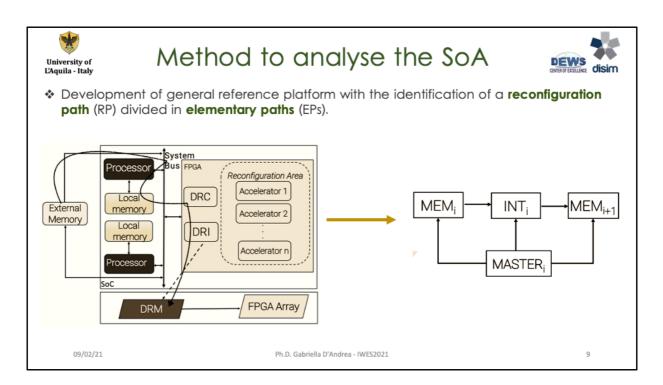

Our DPR time SoA study highlights that does not exist an approach that, considering the whole reconfiguration path (path used to transfer the BS from the external memory to the FPGA reconfiguration memory), allows to calculate in advance the DPR time and it is potentially applicable to all DPR compliant platforms. Hence at this point, we have started working on the reconfiguration path.

We have developed a general reference platform for DPR identifying the reconfiguration path (indicated in the figure with the black arrow) and dividing it into the elementary path (depicted on the right side of the figure).

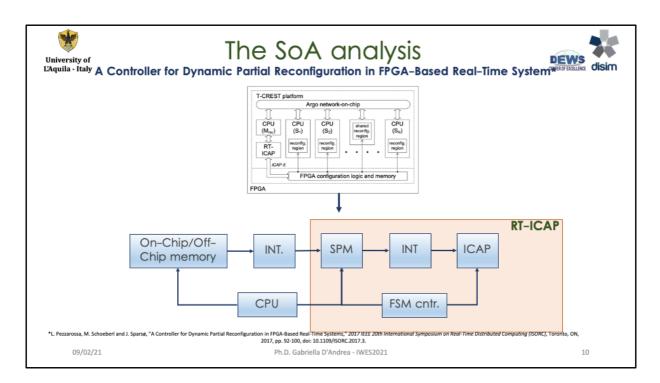

By instantiating the general DPR compliant platform into the works presented in the DPR time SoA we have studied their method to calculate the reconfiguration time.

| * | The SoA analys<br>DPR time that,  |                  |                    | <b>ck</b> of an ap | proach to k | bound the v | contexoFEXELLENCE         |

|---|-----------------------------------|------------------|--------------------|--------------------|-------------|-------------|---------------------------|

|   | <ul> <li>is target ind</li> </ul> | depende          | ent;               |                    |             |             |                           |

|   | <ul> <li>considers a</li> </ul>   | ll the RP        | elements;          |                    |             |             |                           |

|   | • provides a                      | worst-ca         | ise DPR time       | e bound            |             |             |                           |

|   |                                   | _                |                    | dware reso         |             |             |                           |

|   | Approach                          | Target<br>indep. | All RP<br>elements | WCDPRT             | FF          | LUT         | BRAM                      |

|   | CoRQ                              | no               | yes                | yes                | 552         | 631         | 97                        |

|   | RT-ICAP                           | no               | yes                | yes                | 101         | 245         | Encoded<br>Bitstream size |

|   | ZyCAP                             | no               | no                 | no                 | 806         | 620         | 0                         |

|   |                                   |                  |                    |                    |             |             |                           |

Some of the works that we have studied are reported in the table Hardware Resources.

In general most of the studied works require the usage of custom DPR controllers that make them target-dependent increasing both the area occupied in the FPGA and the power consumed.

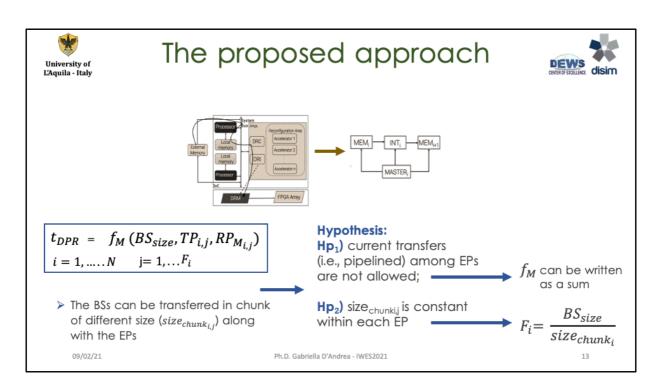

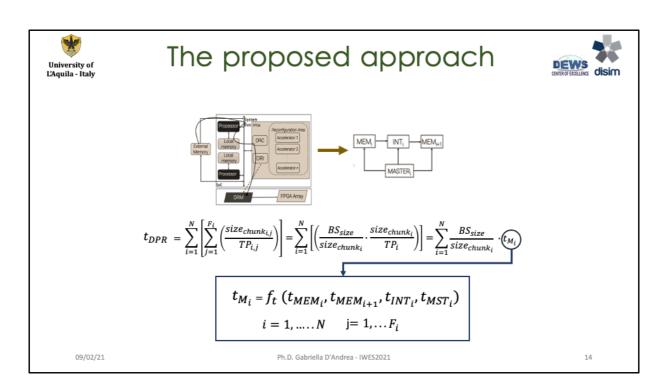

Considering the general DPR compliant platform and the elementary path the DPR time  $(t_{DPR})$  can be calculated with the formula on the left side of the slides; where N is the number of elementary paths (EPs) that compose the reconfiguration path and F<sub>i</sub> is the number of chunks to be transferred within the i-th EP. In the formula,  $t_{DPR}$  is a function  $(f_M)$  of : (i) the BS<sub>size</sub>,(ii) the TP<sub>i,j</sub>, that represents,  $\forall$  EP<sub>i</sub>, the throughput associated to the transfer of each chunk<sub>i,j</sub> within EP<sub>i</sub>, and (iii) RP<sub>Mi,j</sub>, that represents the RP policy adopted to manage the transfer of chunks among adjacent EPs.

Since at design-time we know both the BS size and the chunk size we can calculate the reconfiguration time considering the features of each component of each elementary path. For example, we can consider the size of the memories, or the interconnections frequencies, or the master command queue depth.

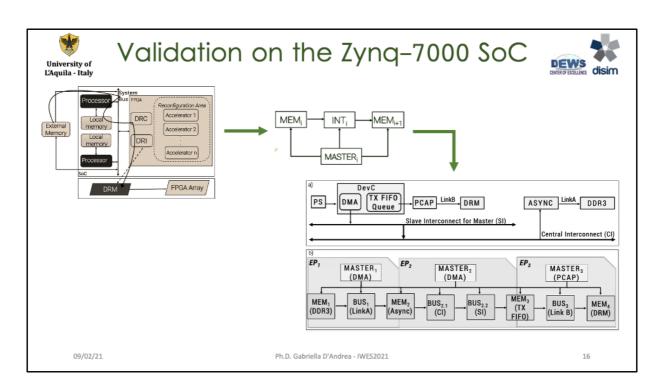

Using the documentations of the Zynq-7000 SoC we have found three elementary paths among which the BS is transferred.

| University of<br>ZAquila - Italy      | Validatio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | n on the                                                                 | e Zyn                                                                        | q-7000                                                    |                                                               |                                     |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------|-------------------------------------|

| a)<br>DevC<br>DMA<br>TX FIF(<br>Queue | Slave Interconnect for Master (SI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IC LinkA DDR3                                                            | $t_{DPR}^{CAL} =$                                                            | $\sum_{i=1}^{N} \frac{BS_{size}}{size_{chunk_i}}  \cdot $ | $t_{M_i} = \sum_{i=1}^{3} \left( \frac{BS_s}{size_c} \right)$ | $\frac{dize}{dunk_i} \cdot t_{M_i}$ |

|                                       | $\begin{array}{c} EP_2 \\ (DMA) \\ HEM_2 \\ HEM_2 \\ HEM_2 \\ (C1) \\ HEM_2 \\ (S1) \\ HEM_2 \\ HEM_2 \\ (S1) \\ HEM_2 \\ HEM$ | MASTER <sub>3</sub><br>(PCAP)<br>1<br>BUS <sub>3</sub><br>(Link B) (DRM) | * ≈                                                                          | $BS_{size} \left( {freq_2} \right)$                       | $\frac{1}{beat_{size_2}} + \frac{1}{BW_{PQ}}$                 | CAP)                                |

| Results for B                         | s <sub>size</sub> = 857740 Bytes ar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ,                                                                        | $t_{DPR}^{(acc\%)}$ ob<br>$t_{DPR}^{CAL} - t_{DPR}^{ACT}$<br>$t_{DPR}^{ACT}$ | 0                                                         | e following form                                              | ula:                                |

|                                       | $beat_{size_2}$ (bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 (worst case)                                                           | 2                                                                            | 3                                                         | 4                                                             |                                     |

|                                       | $t_{DPR}^{CAL} - t_{DPR}^{ACT}$ (ms)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $t_{DPR}^{CAL} - t_{DPR}^{ACT}$ (ms) 2                                   |                                                                              | -2.3                                                      | -2.9                                                          |                                     |

|                                       | acc%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30.3                                                                     | 18.1                                                                         | 34.8                                                      | 43.9                                                          |                                     |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                          |                                                                              | tems," in IEEE Embedded Syste                             |                                                               |                                     |

In this work, considering having exclusive access to the reconfiguration path (i.e., one actor that accesses the memories and the shared buses) we have calculated the DPR time. More details about that approach and the DPR time calculation can be found in our work titled Dynamic Partial Reconfiguration Profitability for Real-Time Systems (G. Valente, T. Di Mascio, G. D'Andrea and L. Pomante, "Dynamic Partial Reconfiguration Profitability for Real-Time Systems Letters, doi: 10.1109/LES.2020.3004302).

| <ul> <li>The proposed</li> <li>is potentia</li> <li>the availal</li> </ul> |                                                      |                                                                           |                                                                                                        |                                                                                                                         |                                                                                                                                                       | CENTER OF EXCELLENCE                                                                                                                                                 |

|----------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                            | ole DPR-                                             | compliant                                                                 |                                                                                                        | e reconfigur                                                                                                            | able paths                                                                                                                                            | in any of                                                                                                                                                            |

| <ul> <li>allows cald</li> </ul>                                            | culating                                             | a WCDPRT                                                                  | suitable in t                                                                                          | he hard rea                                                                                                             | al-time syste                                                                                                                                         | ems domain.                                                                                                                                                          |

|                                                                            |                                                      | Hard                                                                      | ware resour                                                                                            | ces                                                                                                                     |                                                                                                                                                       |                                                                                                                                                                      |

| Approach                                                                   | Target<br>indep.                                     | All RP<br>elements                                                        | WCDPRT                                                                                                 | FF                                                                                                                      | LUT                                                                                                                                                   | BRAM                                                                                                                                                                 |

| CoRQ                                                                       | no                                                   | yes                                                                       | yes                                                                                                    | 552                                                                                                                     | 631                                                                                                                                                   | 97                                                                                                                                                                   |

| RT-ICAP                                                                    | no                                                   | yes                                                                       | yes                                                                                                    | 101                                                                                                                     | 245                                                                                                                                                   | Encoded<br>Bitstream size                                                                                                                                            |

| ZyCAP                                                                      | no                                                   | no                                                                        | no                                                                                                     | 806                                                                                                                     | 620                                                                                                                                                   | 0                                                                                                                                                                    |

| The proposed<br>approach                                                   | Yes                                                  | Yes                                                                       | Yes                                                                                                    | 0                                                                                                                       | 0                                                                                                                                                     | 0                                                                                                                                                                    |

|                                                                            |                                                      |                                                                           |                                                                                                        |                                                                                                                         |                                                                                                                                                       |                                                                                                                                                                      |

|                                                                            |                                                      |                                                                           |                                                                                                        |                                                                                                                         |                                                                                                                                                       |                                                                                                                                                                      |

|                                                                            | Approach<br>CoRQ<br>RT-ICAP<br>ZyCAP<br>The proposed | ApproachTarget<br>indep.CoRQnoRT-ICAPnoZyCAPnoThe proposed<br>approachYes | ApproachTarget<br>indep.All RP<br>elementsCoRQnoyesRT-ICAPnoyesZyCAPnonoThe proposed<br>approachYesYes | ApproachTarget<br>indep.All RP<br>elementsWCDPRTCoRQnoyesyesRT-ICAPnoyesyesZyCAPnononoThe proposed<br>approachYesYesYes | Hardware resourcesApproachTarget<br>indep.All RP<br>elementsWCDPRTFFCoRQnoyesyes552RT-ICAPnoyesyes101ZyCAPnonono806The proposed<br>approachYesYesYes0 | Hardware resourcesApproachTarget<br>indep.All RP<br>elementsWCDPRTFFLUTCoRQnoyesyes552631RT-ICAPnoyesyes101245ZyCAPnonono806620The proposed<br>approachYesYesYesYes0 |