# **IWES 2021**

6th Italian Workshop on Embedded Systems Rome, 9-10 December 2021

# HW/SW Inference-time Optimizations for Reliable Embedded ConvNets

Roberto Giorgio Rizzo

EDA Group - PoliTo

# **Outline**

### Introduction

ConvNets in embedded real-life scenarios: Quality and Performance challenges

## Inference-time optimizations for reliable embedded ConvNets

- AdapTTA: Adaptive Test-Time Augmentation 6

- Improve Quality (i.e., Accuracy) of embedded ConvNets in real-life use

- TVFS: Topology Voltage Frequency Scaling

- <u>Thermal-aware performance management</u> technique for continuous inference of embedded ConvNets on low-power CPUs, under latency constraints

# Introduction

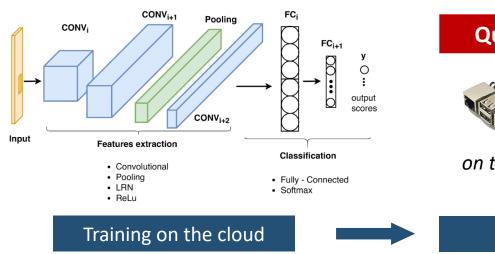

### ConvNets in embedded real-life scenarios

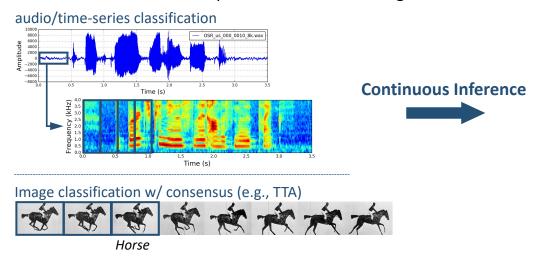

ConvNets state-of-the-arts for several tasks and apps in Computer Vision (also NLP, Time-Series)

### **Quality & Performance Challenges**

on the field -> where the data is collected

Inference on the Edge

### **ConvNets in embedded real-life scenario: Quality challenges**

- Input patterns collected in harsh environment might differ from those used at training time:

- Size & orientation of the objects

- Background

- Lights conditions & contrast

- Model generalization capability at training-time w/ data augmentation is not always sufficient

VS.

No ConvNet fine-tuning (i.e., re-training) w/ data collected on the field

# Training Data No background, vertical orientation

Misled Prediction

Inference real-life collected Data

Complex background, different orientation

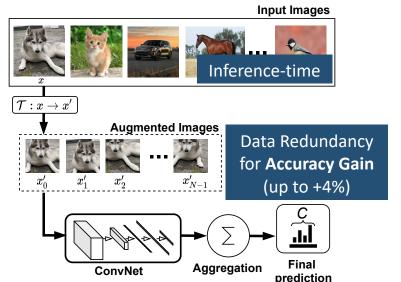

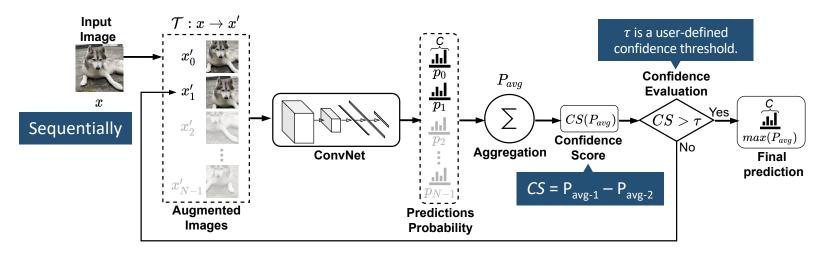

### **Test-Time Augmentation (TTA): main features**

- Improve accuracy with multiple inferences on a set of N input images altered through transforms: Geometric, Luminosity, Contrast, Blur, Channel shuffle, etc.

- Final prediction through a consensus of the aggregated predictions

TTA conceived for **GPUs**: exploit batch inference

Embedded **CPUs**: batch≈*N* proportional

|                 | interestice fatericy (1113) |      |               |                |       |               |  |

|-----------------|-----------------------------|------|---------------|----------------|-------|---------------|--|

|                 | NVIDIA Titan Xp             |      |               | ARM Cortex-A53 |       |               |  |

| ConvNet         | 1                           | 5    | 10            | 1              | 5     | 10            |  |

| MobileNetV1     | 18.2                        | 18.6 | 18.7          | 53.1           | 290.6 | 569.9         |  |

| MobileNetV2     | 12.1                        | 12.4 | 12.9          | 44.2           | 261.8 | 513.5         |  |

| EfficientNet-B0 | 21.3                        | 22.4 | 22.6          | 68.5           | 358.9 | 682.3         |  |

| EfficientNet-B1 | 31.9                        | 33.4 | 33.9          | 103.4          | 536.4 | 1290.2        |  |

|                 |                             |      | $\rightarrow$ |                |       | $\rightarrow$ |  |

$\times 1$

Inference latency (ms)

Minimize this cost

$\times 10$

### From TTA to AdapTTA for Embedded ConvNets: main intuition

- Fixed N transformed images might bee too conservative

- For certain inputs, the key features are well exposed and easy to be detected.

- AdapTTA: a more flexible TTA mechanism exploiting intermediate results

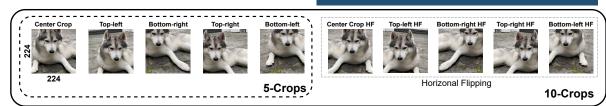

### **Experimental Setup**

Augmentation Policies: 5C e 10C (sota)

More redundancy, higher accuracy

- Hardware Platforms & Compiler Toolchain

- Odroid-C2 [1]:

- 4 Arm Cortex-A53 @ 1.5 GHz

- 1 GB RAM

- TFI ite v1.14

- GNU Toolchain v6.5

**TensorFlow** Lite

Image Classification ConvNet Benchmaks

|     | ConvNet<br>[ImageNet]      | Storage<br>[MB] | Top-1 [%] | L <sub>nom</sub> [ms] |

|-----|----------------------------|-----------------|-----------|-----------------------|

| [2] | MobileNetV1<br>MobileNetV2 | 4.3             | 70.0      | 53.1                  |

|     |                            | 3.4             | 70.8      | 44.2                  |

| [3] | EfficientNet-B0            | 5.4             | 74.4      | 68.5                  |

|     | EfficientNet-B1            | 6.4             | 75.9      | 103.4                 |

<sup>[2]</sup> Tensorflow lite hosted models - https://www.tensorflow.org/lite/guide/hosted models

<sup>[3]</sup> Tensorflow hub - https://tfhub.dev

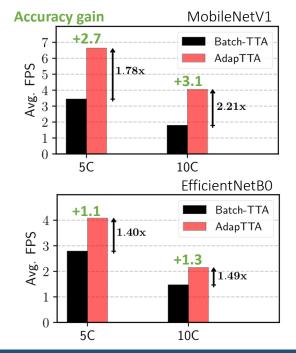

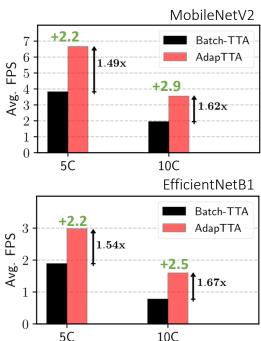

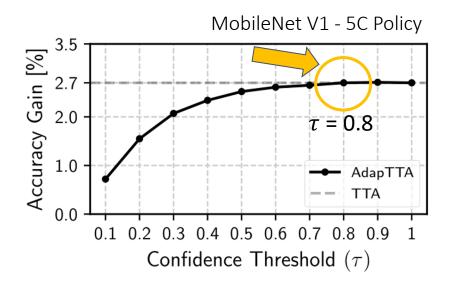

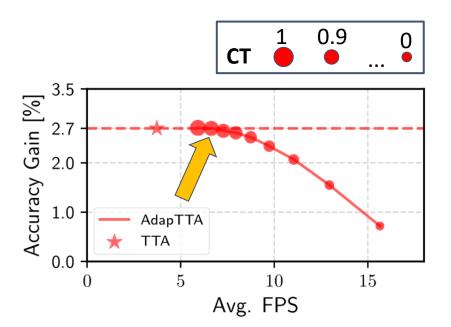

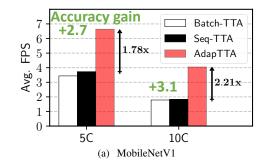

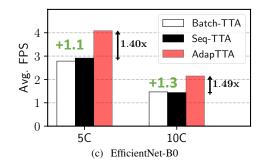

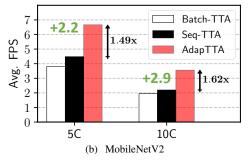

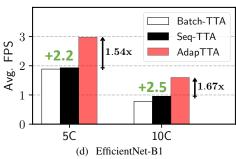

### **Experimental Results**

- ImageNet validation set (50k images)

- Confidence Threshold  $\tau = 0.8$

### Number of inferences (avg)

| ConvNet         | <b>5</b> C | 10C  |

|-----------------|------------|------|

| MobileNetV1     | 2.81       | 4.57 |

| MobileNetV2     | 3.37       | 6.26 |

| EfficientNet-B0 | 3.57       | 6.75 |

| EfficientNet-B1 | 3.24       | 6.02 |

### **More efficient Embedded TTA**

- 1. Accuracy gain at inference-time

- 2. Contained latency overhead

### **ConvNets in embedded real-life scenarios: Performance challenges**

- Deploy **continuous inference** regime with latency constraints:

- Power demanding task: intensive workload at max. frequency

- Embedded systems with limited Thermal Design Power (TDP),

no room for heat spreader or active cooling

on the field

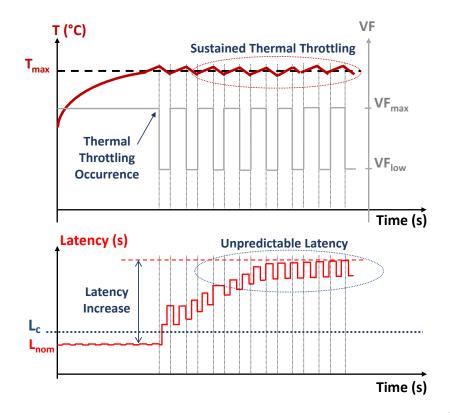

### Thermal-induced performance loss

- Continuous inference of embedded ConvNets on CPUs w/ limited TDP under latency constraint (L<sub>c</sub>)

- Intensive workload at max. frequency (VF<sub>max</sub>) affects the thermal stability

- On-chip temperature oversteps safety threshold  $(T_{max})$  Thermal Throttling

- To avoid irreversible damages,

OS policy lowers core's VF (VF<sub>low</sub>) until

temperature is back to safety

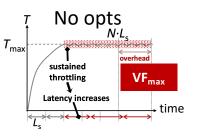

- Repeated thermal throttling leads to performance penalty, thus, latency constraint mismatch

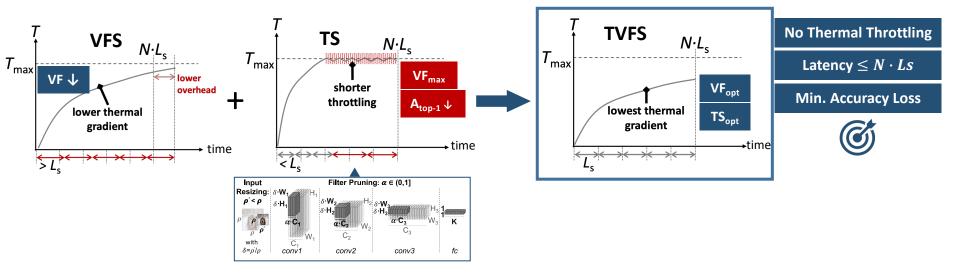

### **Main Idea**

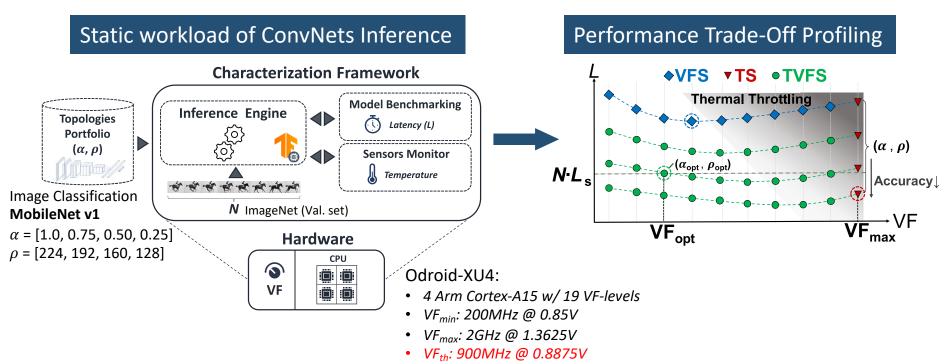

- Thermal-aware performance management through the cooperation of:

- power-reduction techniques -> Voltage-Frequency Scaling (VFS)

- algorithmic optimizations -> ConvNet Topology Scaling (TS)

### **Problem Formulation and Experimental Setup**

# Questions

### **Contacts:**

robertogiorgio.rizzo@polito.it andrea.calimera@polito.it

# References

- "AdapTTA: Adaptive Test-Time Augmentation for Reliable Embedded ConvNets".

L. Mocerino, R. G. Rizzo, V. Peluso, A. Calimera, E. Macii; In: VLSI-SoC 2021.

- "TVFS: Topology Voltage Frequency Scaling for Reliable Embedded ConvNets".

R. G. Rizzo, V. Peluso, A. Calimera. In: IEEE TCAS-II 68 (2), 672-676 (2020)

- "Performance profiling of embedded convnets under thermal-aware DVFS".

V. Peluso, R. G. Rizzo, A. Calimera. In: Electronics 8 (12), 1423 (2020)

- "Efficacy of topology scaling for temperature and latency constrained embedded convnets". V. Peluso, **R. G. Rizzo**, A. Calimera. In: Journal of Low Power Electronics and Applications 10 (1), 10 (2020).

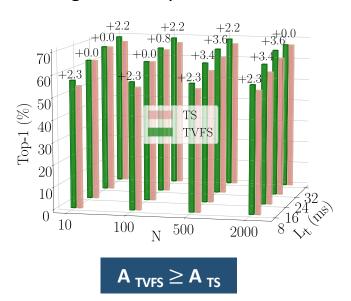

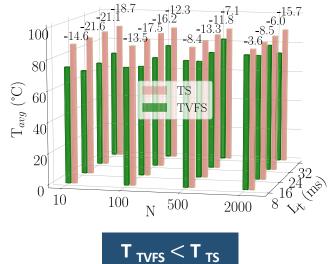

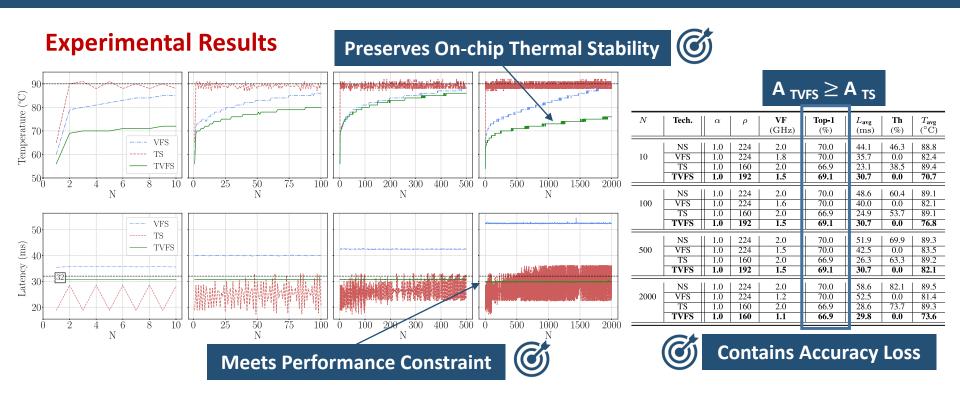

### **Experimental Results**

Calibration set: ImageNet val (1k images)

### **Experimental Results**

- ImageNet validation set (50k images)

- Confidence Threshold  $\tau = 0.8$

### **Experimental Results**

More stringent latency constraints